The netX family

The netX chips combine leading edge communication with hardware platforms for different applications. We want to enable our customers to focus completely on their specific application know-how and use the unique capabilities of our hardware platforms to differentiate their products in the market.

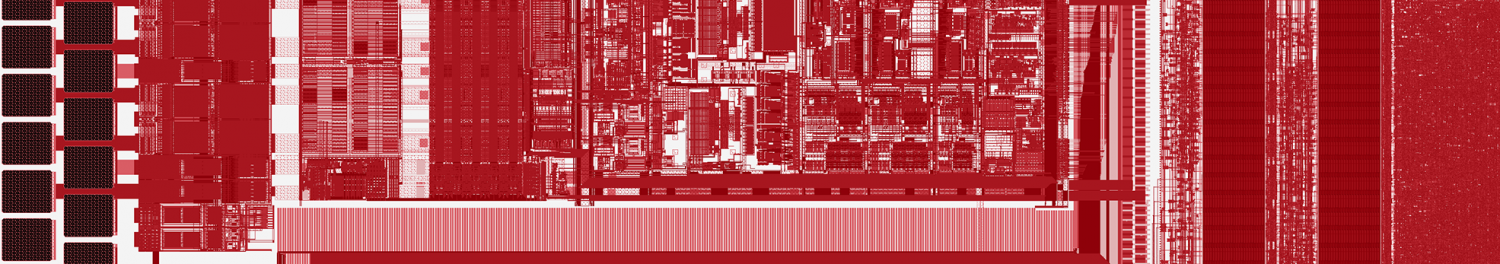

All netX chips are based on Hilscher’s XC module, which is a programmable unit to handle all major Fieldbusses and Real-Time-Ethernet communication standards. Ring structures typically used in Real-Time-Ethernet require 2 XC channels (e.g. PROFINET IRT, EtherCAT, Sercos III), while most Fieldbusses only need one XC channel (e.g. PROFIBUS, ASi, CAN). Some “Soft Real-Time-Ethernet” standards also only require one XC channel (e.g. PROFINET RT, EtherNet/IP). XC-Gen2 is the second generation of XC modules developed to handle PROFINET IRT V2.3. It uses a dual-processor structure (similar to the second generation of Siemens’ controller ERTEC 200P).

Since netX4000 the netX chips include crypto acceleration to support Industrial IoT / Industry 4.0.

| Device | Description | Specialties | Year | XC-Channels | System CPU | Nr of CPU Cores | Tech node | integrated RAM (kByte) | ETH PHY | Interfaces | Crypto Core | Package (mm²) |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| netX 500 / netX 100 | 4 channel network controller for Fieldbus and RT-Ethernet master and slaves | 4 channels + Powerfull CPU for Master Communication, MMU + Display Controller | 2005 | 4 | ARM 926 @200MHz | 13 | 150nm | 248 | 2 | USB, UART, SPI, I2C, Display Controller, ADC | – | BGA 345 (22 x 22) |

| netX 50 | Network controller for Fieldbus and RT-Ethernet slaves | Integrated communication with Ethernet PHY and protocol stack | 2008 | 2 | ARM 966 @200MHz | 7 | 150nm | 148 | 2 | USB,3x UART, 2xSPI, 2xI2C, 8x IO-Link | – | BGA 324 (19 x 19) |

| netX 5 | Network processor for Fieldbus and RT-Ethernet | No PHY, no CPU for protocol stack | 2009 | 2 | – | 7 | 180nm | 100 | – | SPI | – | BGA 201 (13 x 13) |

| netX 10 | Network controller for Fieldbus and Soft-RT-Ethernet | Single XC, no ext. SDRAM required | 2010 | 1 | ARM 966 @100MHz | 5 | 150nm | 142 | 1 | SPI, SQI, 2x UART, I2C, USB1.1, 4x IO-Link, ADC | – | BGA 197 (13 x 13) |

| netX 51 | Network controller for Fieldbus and RT-Ethernet slaves with external memory | XC Gen2, pin compatible to netX 50 | 2012 | 2 (Gen2) | ARM 966 @100MHz | 10 | 150nm | 740 | 2 | SPI, SQI, 3x UART, 2x I2C, CAN, ETH MAC, USB1.1 | – | BGA 324 (19 x 19) |

| netX 52 | Network controller for Fieldbus and RT-Ethernet slaves | XC Gen2 without external SDRAM | 2012 | 2 (Gen2) | ARM 966 @100MHz | 10 | 150nm | 740 | 2 | SPI, SQI, 3x UART, 2x I2C, CAN, ETH MAC, USB1.1 | – | BGA 244 (15 x 15) |

| netX 6 | Network processor for Fieldbus and RT-Ethernet | netX 52 without ARM, RAM reduced | 2013 | 2 (Gen2) | xPIC | 9 | 150nm | 276 | 2 | SPI, SQI, 3x UART, 2x I2C, CAN, ETH MAC, USB1.1 | – | BGA 244 (15 x 15) |

| netX 4000 | Automation Platform on Chip | Dual A9 system for Android and Linux | 2017 | 4 (Gen2) | Communciation: ARM Cortex R7 @400MHz

Application: |

23 | 40nm | 3208 | 2 | 2x GMAC, MAC, 4x SPI, SQI, 9x I2C, 3x I2S, 8x UART, 4x CAN, 8x IO-Link, 2x USB2, USB1.1, PCIe, SDIO, 2x Display Controller, ADC | DES, AES, SHA, MD5 | BGA 596 (27 x 27) |

| netX 4100 | 4 channel network controller for Fieldbus and RT-Ethernet master and slaves | XC Gen2 successor of netX 500 | 2017 | 4 (Gen2) | ARM Cortex R7 @400MHz | 21 | 40nm | 3080 | 2 | 2x GMAC, MAC, 2x SPI, SQI, 3x I2C, 4x UART, 1x CAN, 8x IO-Link, USB1.1, PCIe, SDIO, Display Controller, ADC | DES, AES, SHA, MD5 | BGA 420 (23 x 23) |

| netX 90 | Smallest fully integrated multiprotocoll SoC | 1.5MB Flash Ethernet PHY DCDC core supply separated application CPU System |

2018 | 2 (Gen2) | Communication: ARM Cortex M4 @100MHz Application: |

12 | 90nm | 724 | 2 | ETH MAC, 3x UART, 4x SPI, SQI, 4x I2C, 2x CAN, 8x IO-Link, 2x BISS, 2x EnDat, ADC | ECC, RSA, AES, SHA, MD5 | BGA 144 (10 x 10) |

Note: Most netX chips integrate the Ethernet PHY, which explains an addon of ~600mW in power dissipation when activated.